semiconductors/chip-design

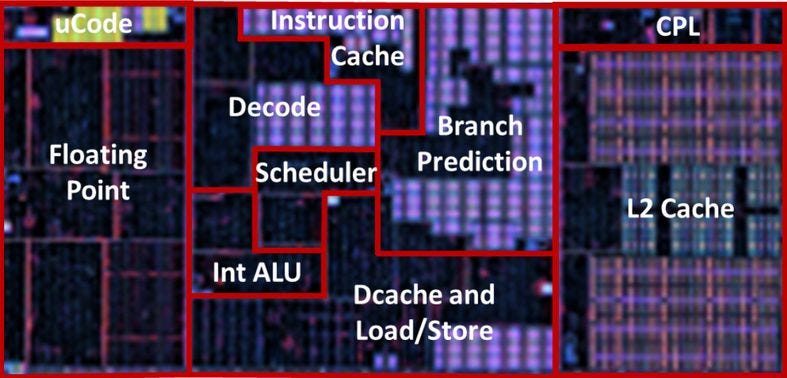

Most people think of machine instructions as the fundamental steps that a computer performs. However, many processors have another layer of ...

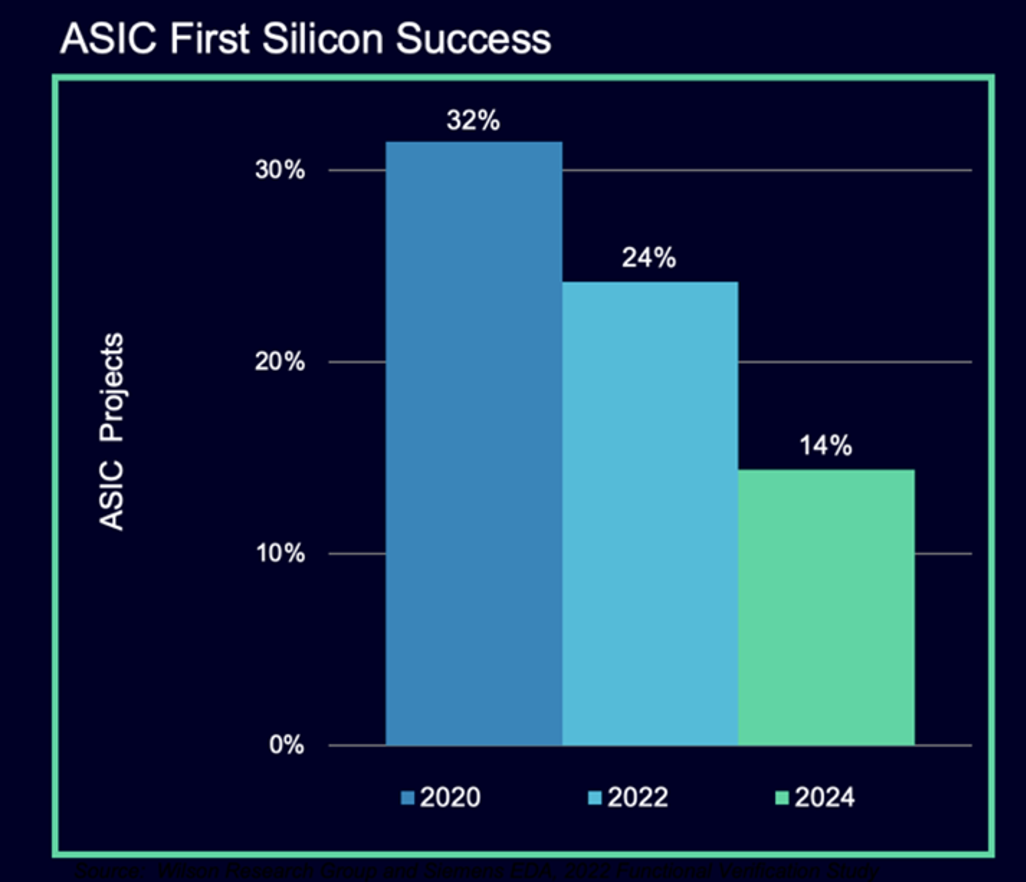

Number of designs that are late increases. Rapidly rising complexity is the leading cause, but tools, training, and workflows need to improve.

[vc_row][vc_column column_width_percent=”90″ gutter_size=”3″ overlay_alpha=”50″ shift_x=”0″ shift_y=”0″ shift_y_down=”0″ z_index=”0″ medium_width=”0″ mobile_width=”0″ width=”1/1″ uncode_shortcode_id=”158708″][vc_column_text uncode_shortcode_id=”154284″] Conventional wisdom in semiconductor manufacturing has long […]

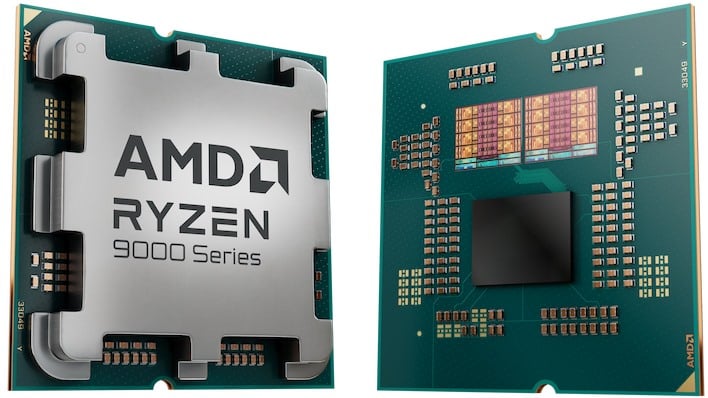

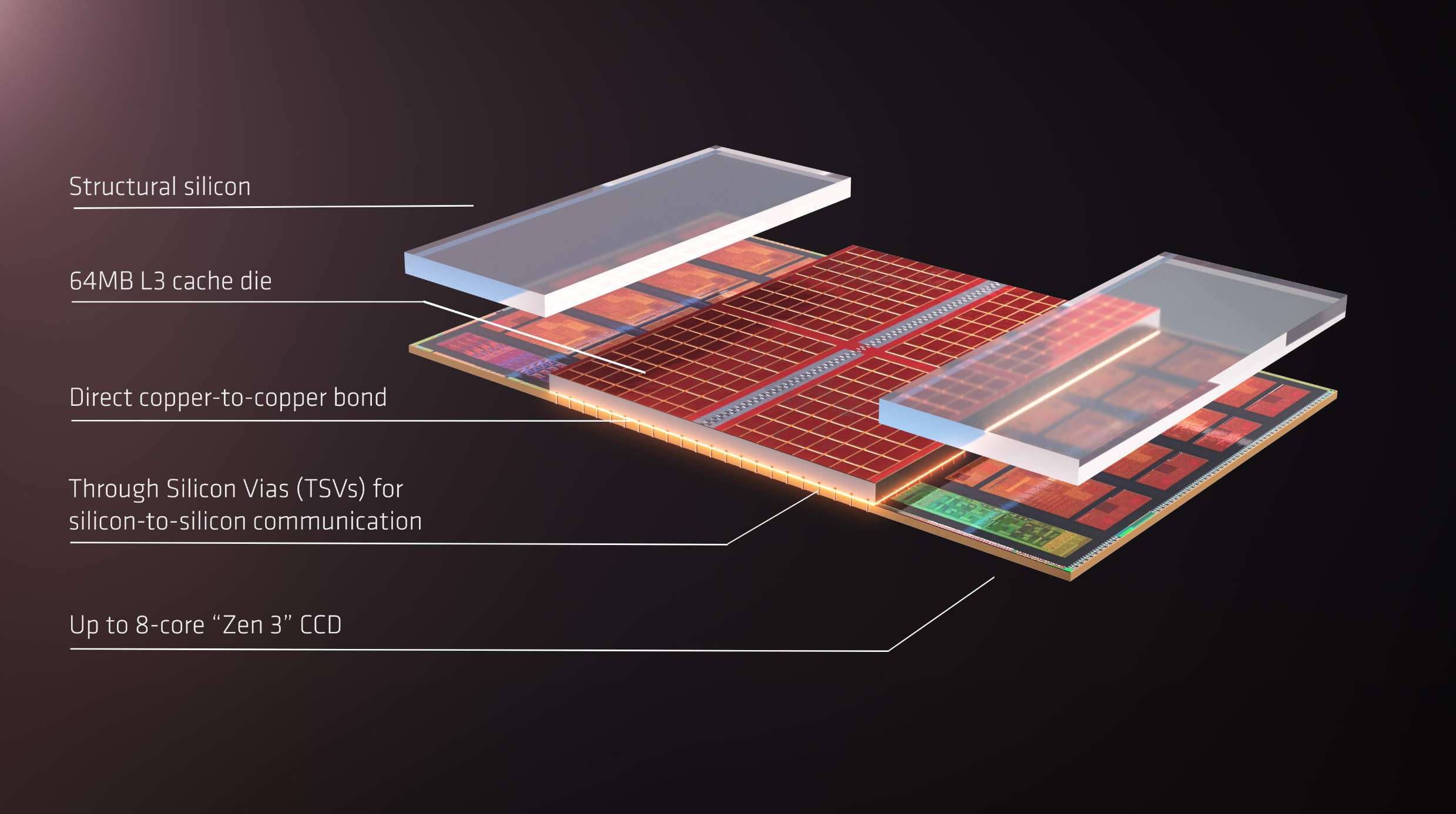

After persistent rumors refused to recede, AMD steps in with a clear explanation why dual-CCD V-Cache doesn't exist.

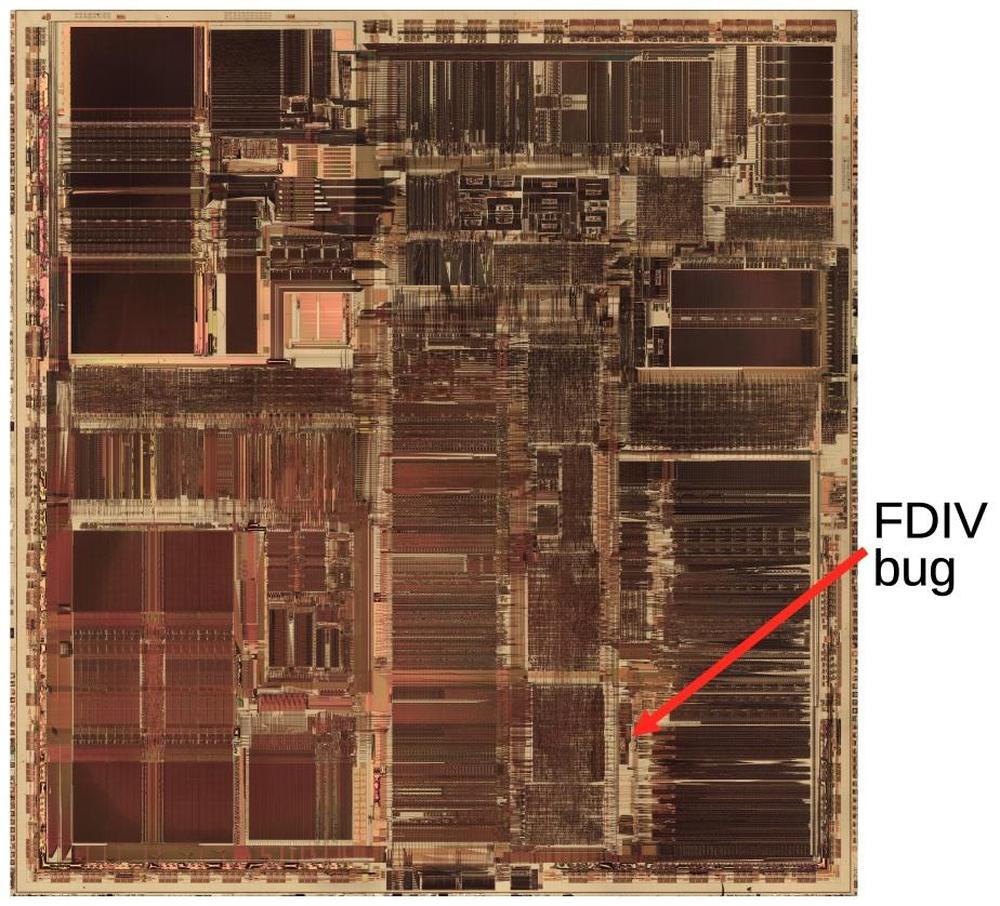

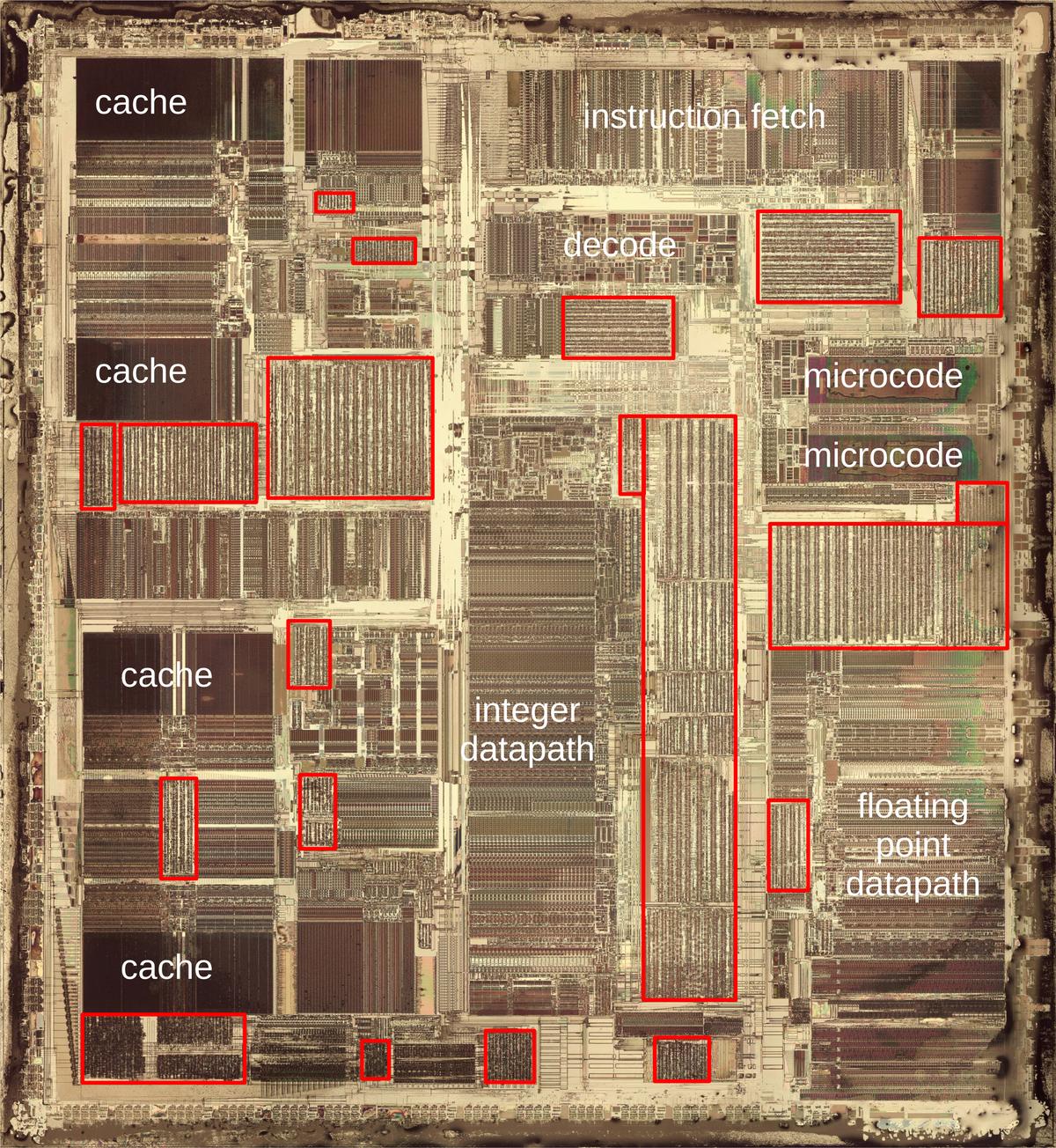

In 1993, Intel released the high-performance Pentium processor, the start of the long-running Pentium line. The Pentium had many improvement...

Large Language Models (LLMs) have become a cornerstone of artificial intelligence, driving advancements in natural language processing and decision-making tasks. However, their extensive power demands, resulting from high computational overhead and frequent external memory access, significantly hinder their scalability and deployment, especially in energy-constrained environments such as edge devices. This escalates the cost of operation while also limiting accessibility to these LLMs, which therefore calls for energy-efficient approaches designed to handle billion-parameter models. Current approaches to reduce the computational and memory needs of LLMs are based either on general-purpose processors or on GPUs, with a combination of weight quantization and

A loop buffer sits at a CPU's frontend, where it holds a small number of previously fetched instructions.

I was studying the silicon die of the Pentium processor and noticed some puzzling structures where signal lines were connected to the silico...

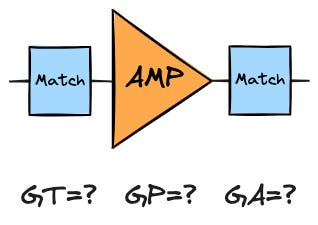

Transducer, Unilateral, Available and Power Gain; what they mean and how to calculate them.

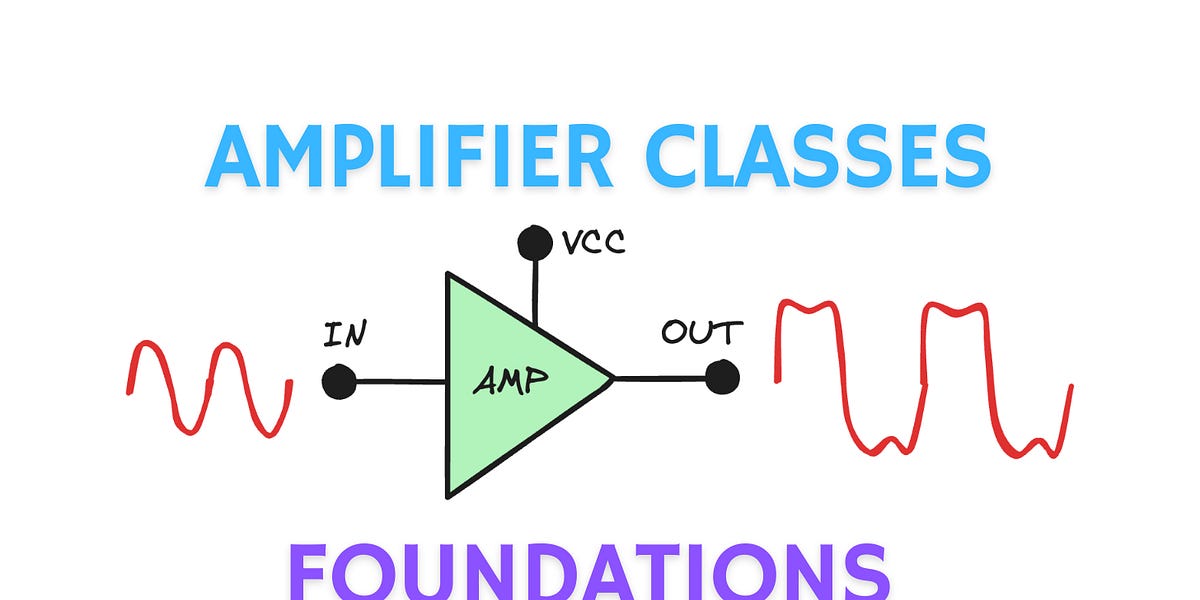

Basic concepts required to understand classes of operation in power amplifiers.

When I recently interviewed Mike Clark, he told me, “…you’ll see the actual foundational lift play out in the future on Zen 6, even though it was really Zen 5 that set the table for that.” And at that same Zen 5 architecture event, AMD’s Chief Technology Officer Mark Papermaster said, “Zen 5 is a ground-up redesign of the Zen architecture,” which has brought numerous and impactful changes to the design of the core.

Intel released the powerful Pentium processor in 1993, a chip to "separate the really power-hungry folks from ordinary mortals." The origin...

A technical paper titled “Basilisk: Achieving Competitive Performance with Open EDA Tools on an Open-Source Linux-Capable RISC-V SoC” was published by researchers at ETH Zurich and University of Bologna. Abstract: “We introduce Basilisk, an optimized application-specific integrated circuit (ASIC) implementation and design flow building on the end-to-end open-source Iguana system-on-chip (SoC). We present enhancements to... » read more

This paper aims to provide insights into the thermal, analog, and RF attributes, as well as a novel modeling methodology, for the FinFET at the industry standard 5nm CMOS technology node. Thermal characterization shows that for a 165K change in temperature, the Sub-threshold Slope (SS) and threshold voltage vary by 69 % and ~70 mV, respectively. At room temperature, a single gate contacted n-FinFET RF device exhibits a cutoff and maximum oscillation frequency of ~100 GHz and ~170 GHz, respectively. Analog and RF Figures of Merit (FoMs) for 5 nm technology at a device level and their temperature sensitivity are also reported. The industry standard BSIM-CMG model is modified to capture the impact of self-heating (SH) and parasitics. The SH model is based on measured data, and the modeling approach renders it independent of other model parameters. To the authors’ knowledge, an iteration free approach to develop a model-card for RF applications is explained for the very first time. Excellent agreement between the measured data and the model indicates that our methodology is accurate and can be used for faster PDK development.

In semiconductor design, “sign-off” during the tape-out (tapeout) of a chip refers to the formal approval process to ensure that the chip design is error-free, meets all specifications, and is ready for manufacturing at the foundry. It is essential because it minimizes the risk of costly errors, ensures compliance with foundry requirements, and validates that

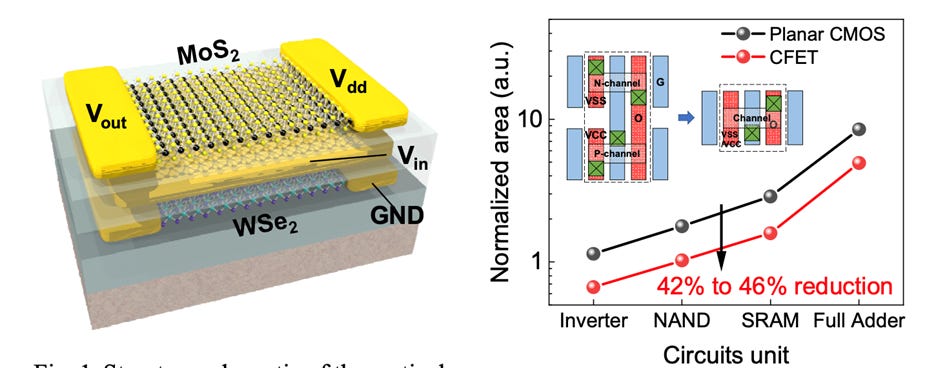

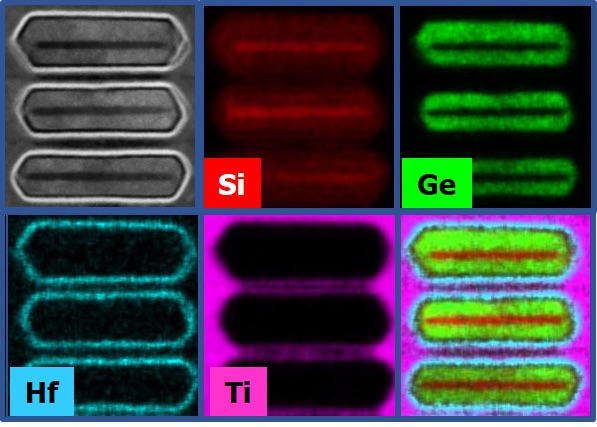

Planar to FinFET to Nanosheet to Complementary FET to 2D

Study tries to settle a bitter disagreement over Google’s chip design AI

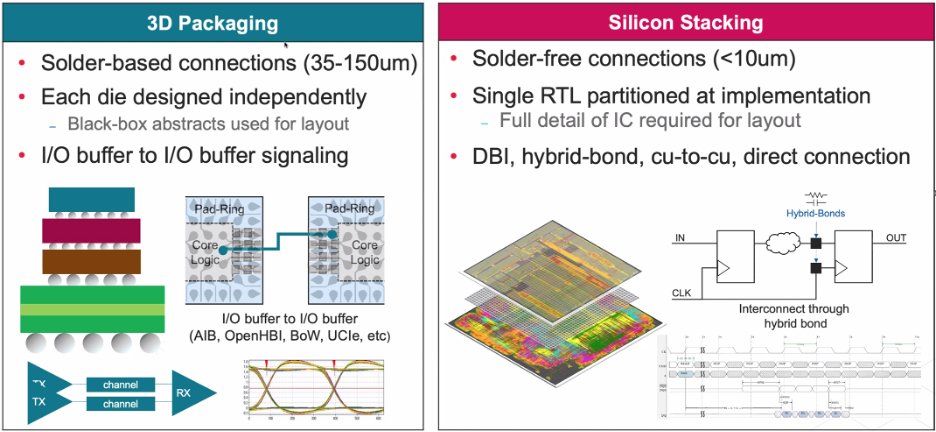

While terms often are used interchangeably, they are very different technologies with different challenges.

RDL, an abbreviation for Redistribution Layer, that is, to make one or more layers of metal on the active chip side to redistribute the pins of the chip.

Historically Intel put all its cumulative chip knowledge to work advancing Moore's Law and applying those learnings to its future CPUs. Today, some of

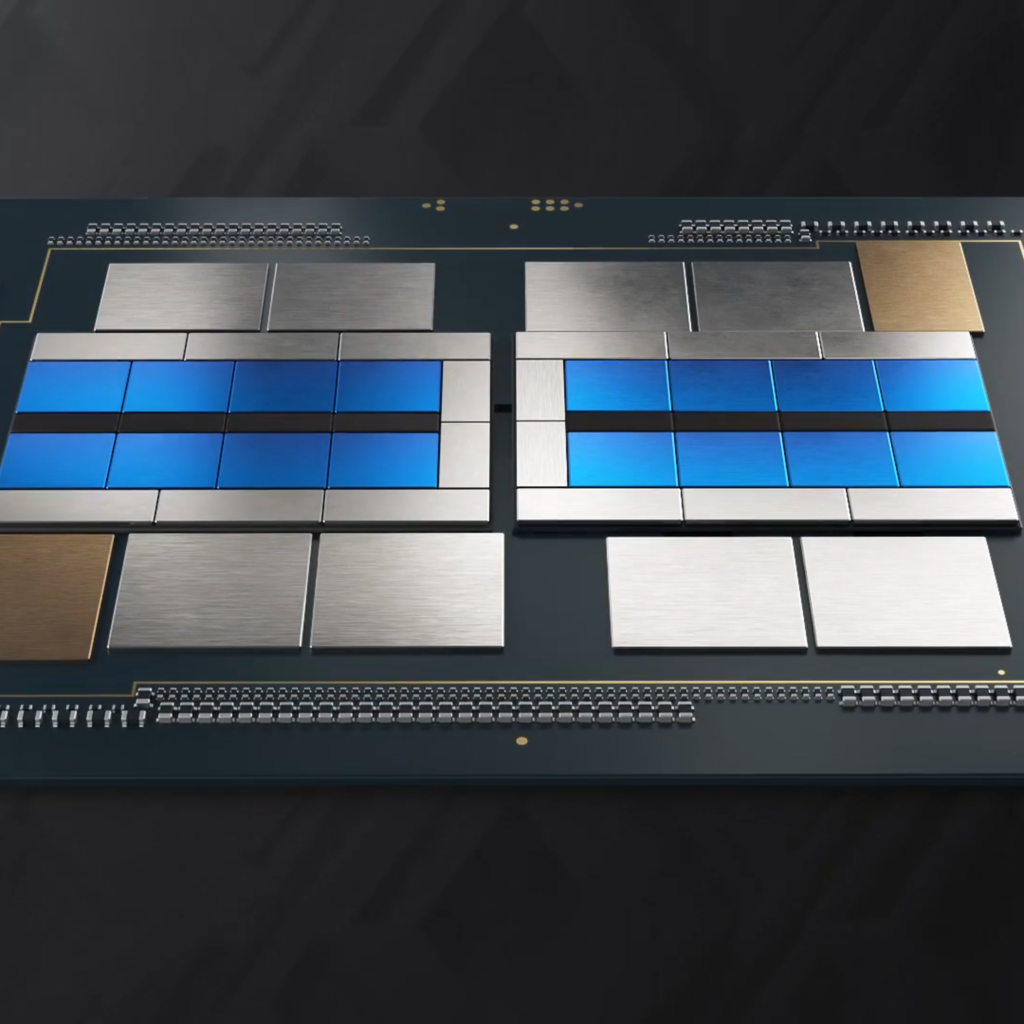

Intel's multi-die interconnect bridge (EMIB) is an approach to in-package high-density interconnect of heterogeneous chips.

Powered by the promises of the CHIPS Act, Intel is investing more than $100 billion to increase domestic chip manufacturing capacity and capabilities.

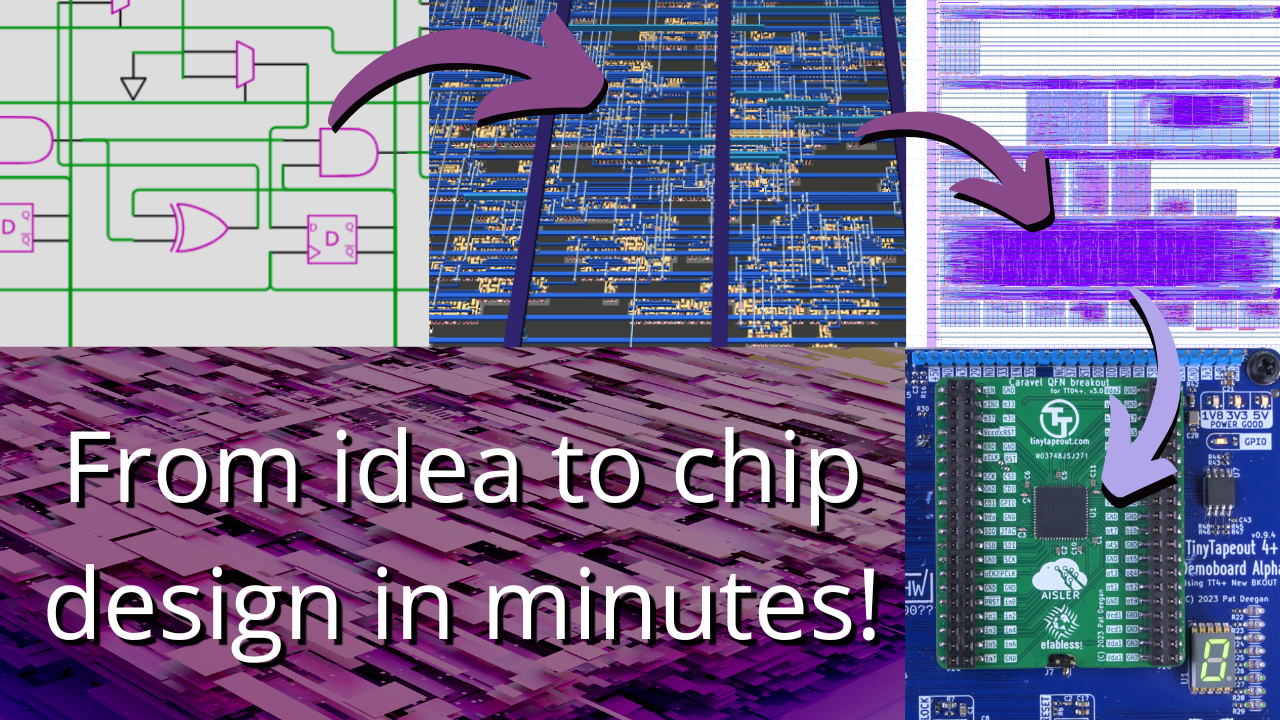

From idea to chip design in minutes! TT09 Closes in TT09 Closes in 44 DAYS 44 HOURS 44 MINS 44 SECS Tiles PCBs Tiny Tapeout is an educational project that makes it easier and cheaper than ever to get your designs manufactured on a real chip! Read the paper here. See what other people are making by taking a look at what was submitted on our previous shuttles.

A new technical paper titled “APOSTLE: Asynchronously Parallel Optimization for Sizing Analog Transistors Using DNN Learning” was published by researchers at UT Austin and Analog Devices. Abstract “Analog circuit sizing is a high-cost process in terms of the manual effort invested and the computation time spent. With rapidly developing technology and high market demand, bringing... » read more

AI firm Synopsys has announced that its DSO.ai tool has successfully aided in the design of 100 chips, and it expects that upward trend to continue.

Book repository "Analysis and Design of Elementary MOS Amplifier Stages" - bmurmann/Book-on-MOS-stages

The following is a list of my articles on various topics. Besides technical articles, news pieces that might have useful technical information are also included. You can find my articles on FPGA...

Learn about voltage waves and how they relate to an important basic concept of radio frequency (RF) circuit design: transmission lines.

Interconnects—those sometimes nanometers-wide metal wires that link transistors into circuits on an IC—are in need of a major overhaul. And as chip fabs march toward the outer reaches of Moore’s Law, interconnects are also becoming the industry’s choke point.

Book repository "Analysis and Design of Elementary MOS Amplifier Stages" - bmurmann/Book-on-MOS-stages

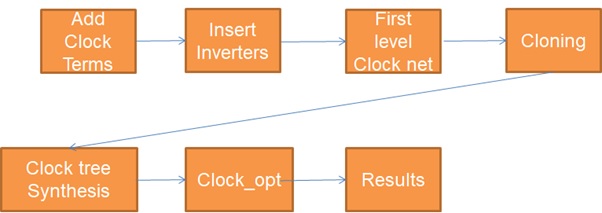

A vast majority of modern digital integrated circuits are synchronous designs. They rely on storage elements called registers or flip-flops, all of which change their stored data in a lockstep manner with respect to a control signal called the clock. In many ways, the clock signal is like blood flowing through the veins of a

The high frequencies and data rates involved in 5G designs makes layout verification all the more important.

New technical paper titled “Bridging the Gap between Design and Simulation of Low-Voltage CMOS Circuits” from researchers at Federal University of Santa Catarina, Brazil. Abstract “This work proposes a truly compact MOSFET model that contains only four parameters to assist an integrated circuits (IC) designer in a design by hand. The four-parameter model (4PM) is... » read more

New technical paper titled “A Review on Transient Thermal Management of Electronic Devices” from researchers at Indian Institute of Technology Bombay. Abstract “Much effort in the area of electronics thermal management has focused on developing cooling solutions that cater to steady-state operation. However, electronic devices are increasingly being used in applications involving time-varying workloads. These... » read more

The researchers are considered a key to the company’s future. But they have had a hard time shaking infighting and controversy over a variety of issues.

When you’re baking a cake, it’s hard to know when the inside is in the state you want it to be. The same is true—with much higher stakes—for microelectronic chips: How can engineers confirm that what’s inside has truly met the intent of the designers? How can a semiconductor design company tell wh

An integrated cache and memory access time, cycle time, area, leakage, and dynamic power model - HewlettPackard/cacti

Silvaco provides standard cell library design and optimization services

I have written a lot of articles looking at leading…

SoC clock tree overview, metrics that help qualify a clock tree and most commonly used clock tree distribution methodologies.

Some things will get better from a design perspective, while others will be worse.

New interconnects offer speed improvements, but tradeoffs include higher cost, complexity, and new manufacturing challenges.

Clock Gating is defined as: “Clock gating is a technique/methodology to turn off the clock to certain parts of the digital design when not needed”. The Need for Clock Gating With most of the SoCs heavily constrained by power budgets, it is of utmost importance to reduce power consumption as much as possible

Leakage current can contribute to power dissipation, especially at lower threshold voltages. Learn about six types of leakage current that can be found in MOS transistors.

Gate-all-around FETs will replace finFETs, but the transition will be costly and difficult.

How can you calculate the number of dies per wafer? A free online tool, DPW equation and reference to two other DPW calculators. Trusted by Amkor and GF.

Static Timing Analysis? Read here the best overview to STA, including theory, real examples, ilustrations, tips and tricks.

In this article, we’ll discuss another group of thermal data, called thermal characterization parameters denoted by the Greek letter Psi (Ψ).

DIE YIELD CALCULATOR Use this online calculator to figure out die yield using Murphy’s model. You’ll need to know the die size, wafer diameter, and defect density. iSine is your complete resource for ASIC design – from concept to manufacturing and testing. We have expertise in system architecture, VHDL, Verilog, gate arrays, mixed signal, full...

Learn about an important thermal metric for designing the interface between an IC package and a heat sink.

Watch the thermal measurement, junction-to-case thermal resistance, in action as we use it to calculate the thermal considerations for a given system.

Engineers must keep pace with advanced IC packaging technology as it evolves rapidly, starting with understanding the basic terms.

Assessing the thermal performance of an IC package becomes easier if you understand this common, but often misapplied, parameter known as theta JA.

In this article, we will learn how to find the optimal size of a transistor/logic gate present in a larger circuit to provide the desired performance using the linear delay model.

When they were first commercialized at the 22 nm node, finFETs represented a revolutionary change to the way we build transistors, the tiny switches in the “brains” of a chip. As compared to...

In this article, we'll discuss the Elmore delay model, which provides a simplistic delay analysis that avoids time-consuming numerical integration/differential equations of an RC network.

The semiconductor industry growth is increasing exponentially with high speed…

Looking at a typical SoC design today it's likely to…

Single-clock design is not always as easy as it seems.

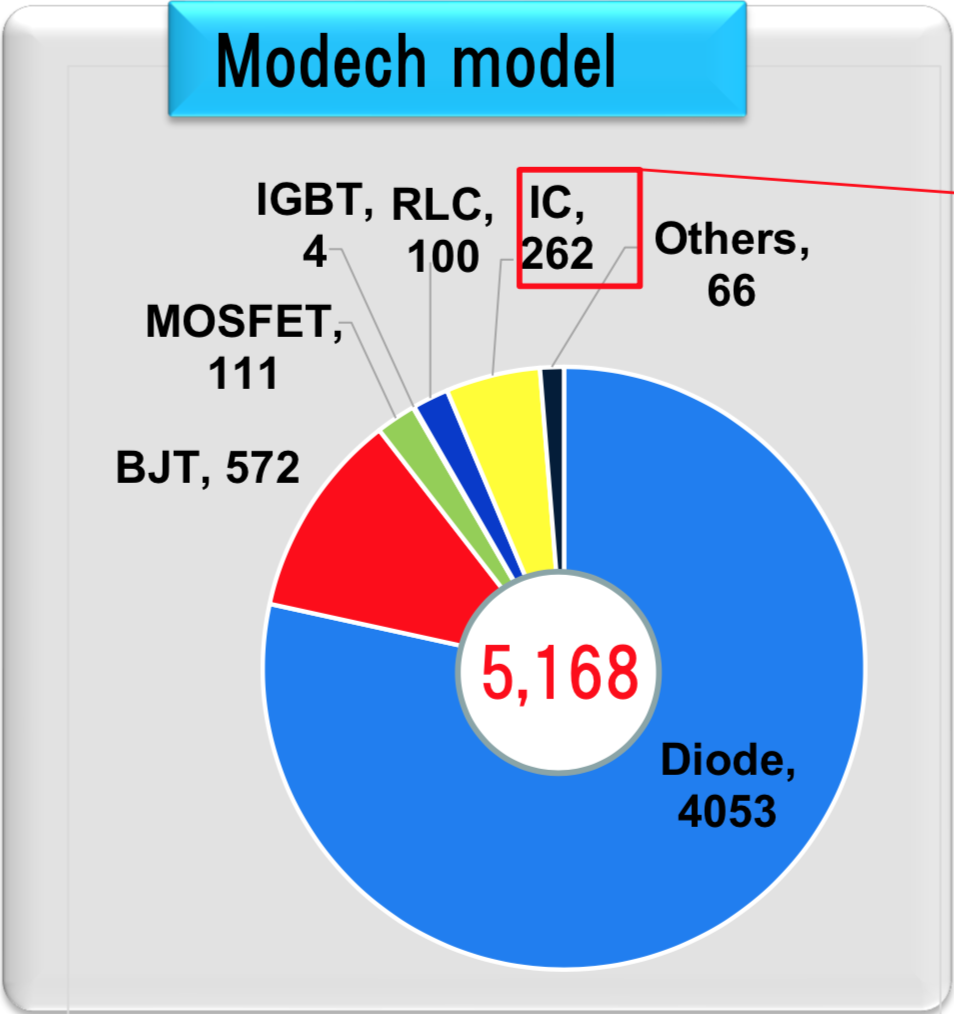

SPICE (Simulation Program with Integrated Circuit Emphasis) is an open-source analog electronic circuit simulator. | SPICE is undoubtedly one of the most popular modeling libraries available, and Japanese e-commerce company MoDeCH is seeking to make the power of SPICE available to everyone.

Accurately determine parasitic effects with the proper set up of two different methods.

Process Corner Explosion, At 7nm and below, modeling what will actually show up in silicon is a lot more complicated.

Post date: Sep 19, 2014 10:01:08 PM

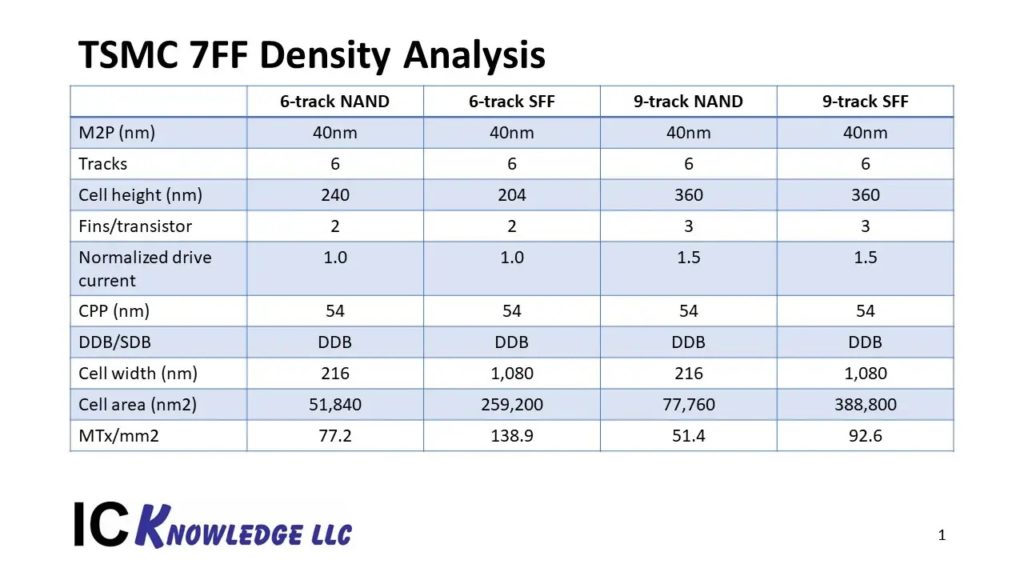

Fab Cost, WFE Implications, Backside Power Details