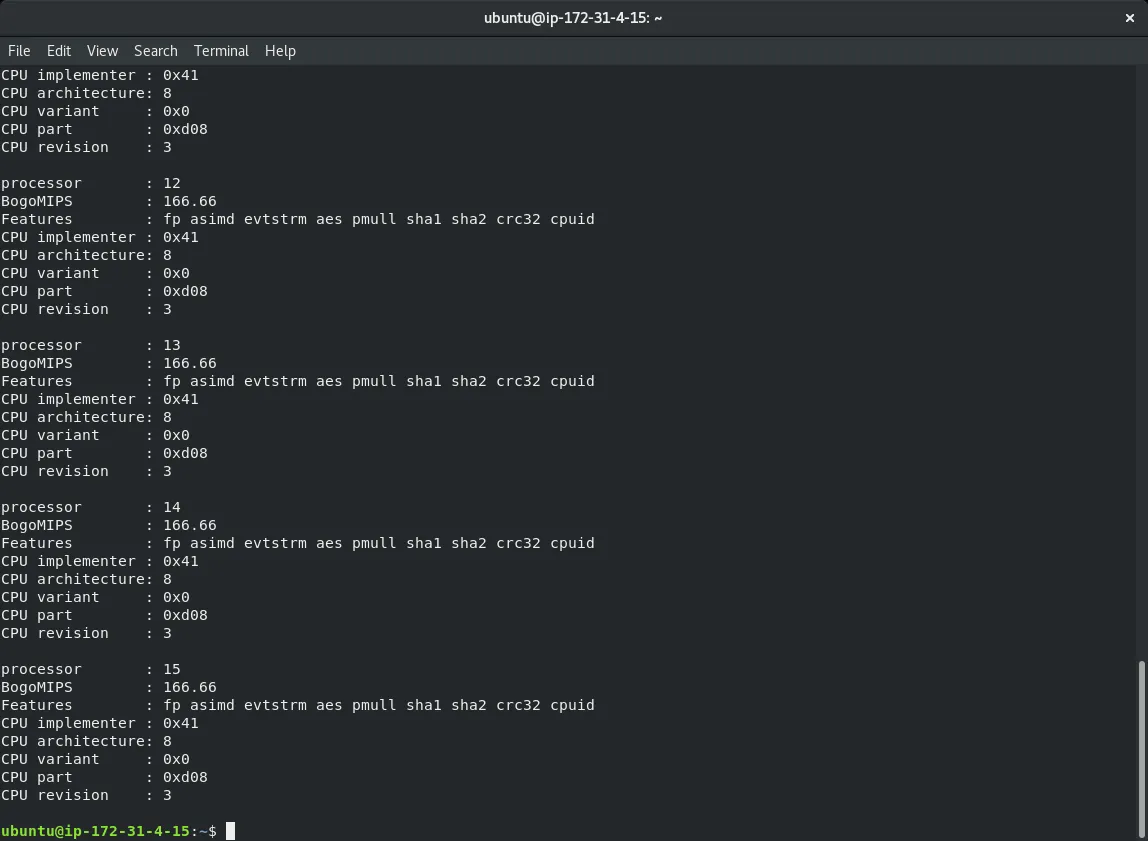

cpus

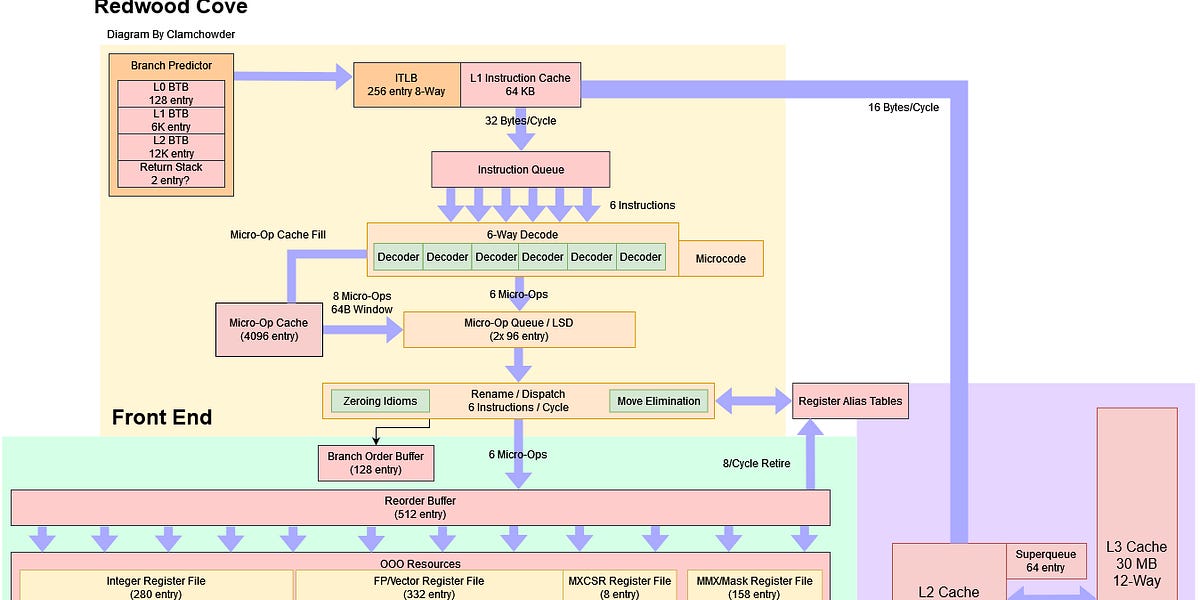

Most people think of machine instructions as the fundamental steps that a computer performs. However, many processors have another layer of ...

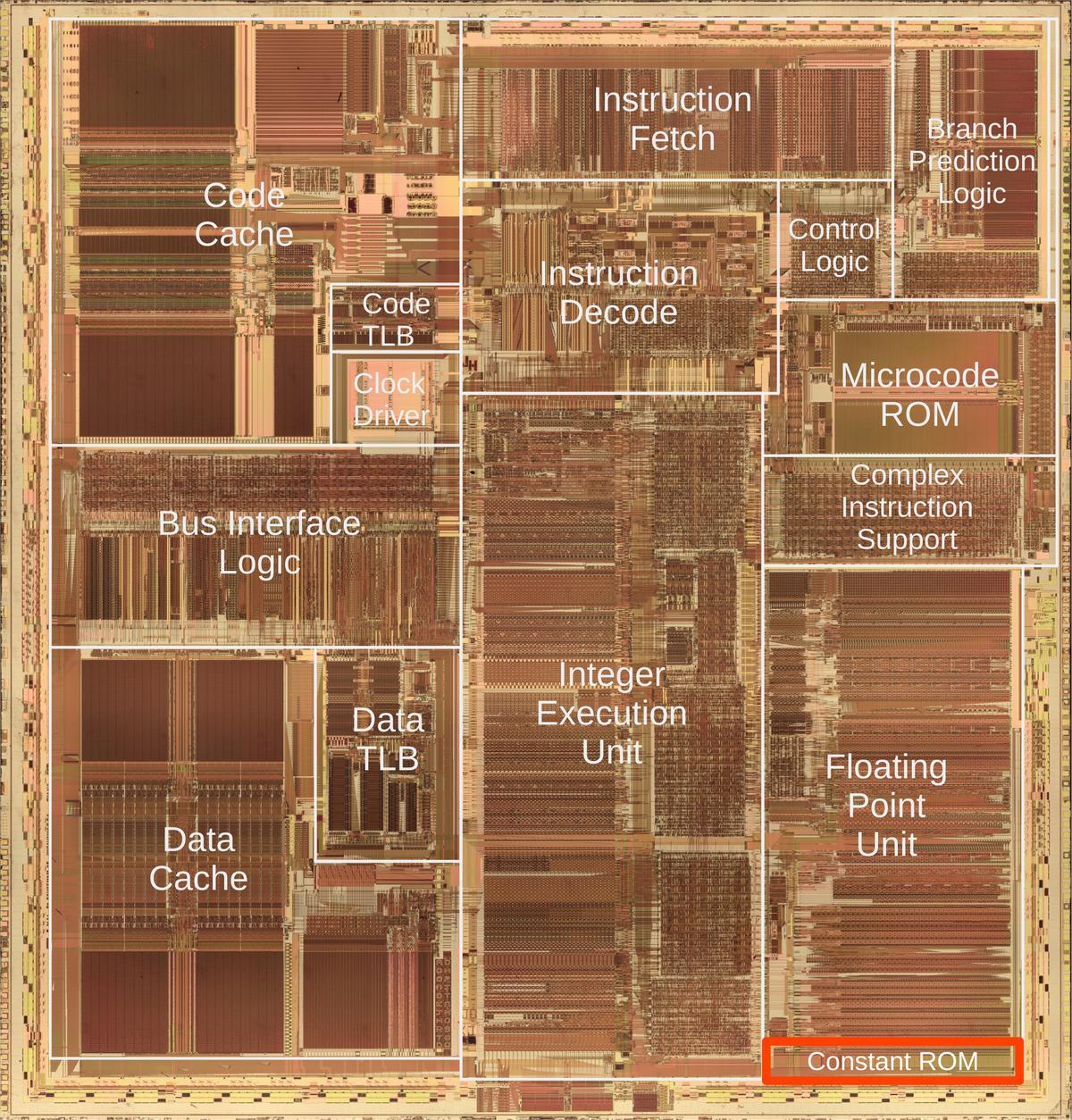

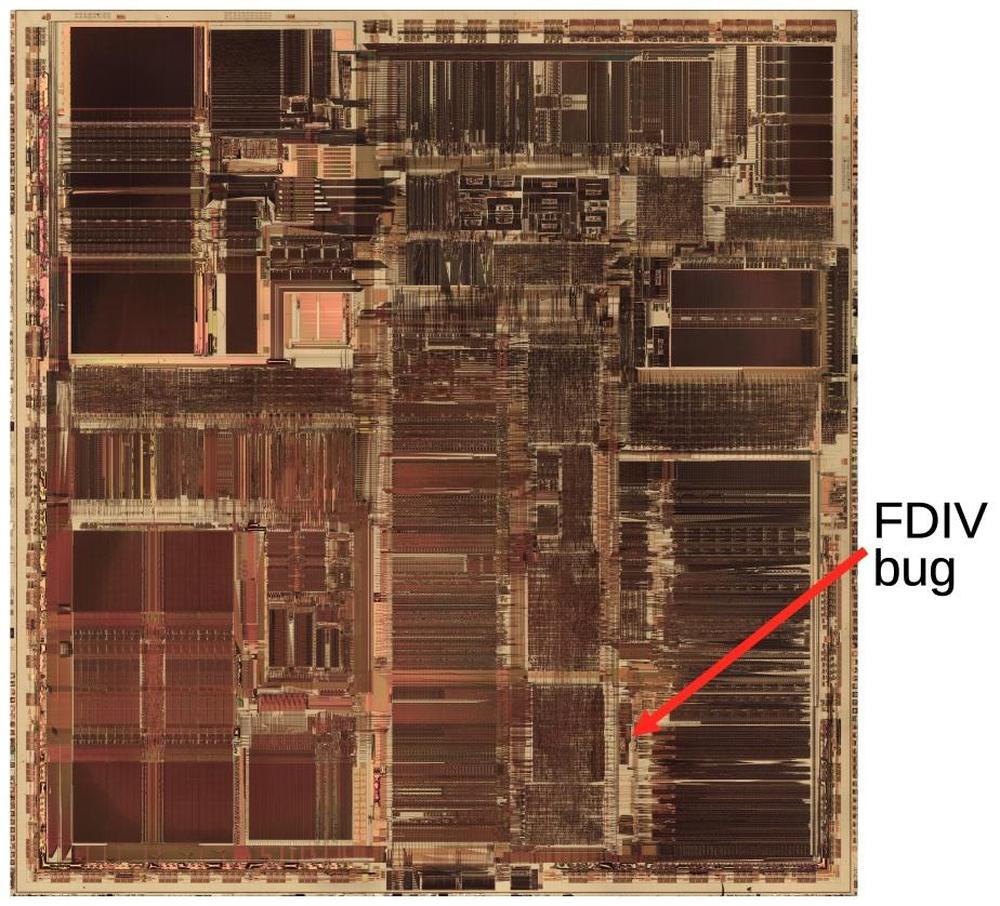

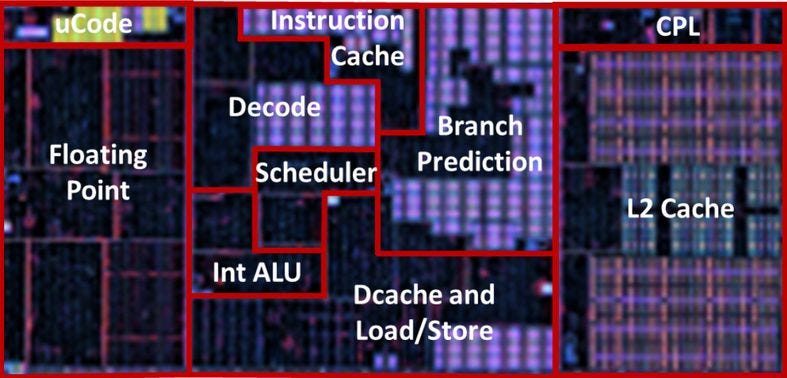

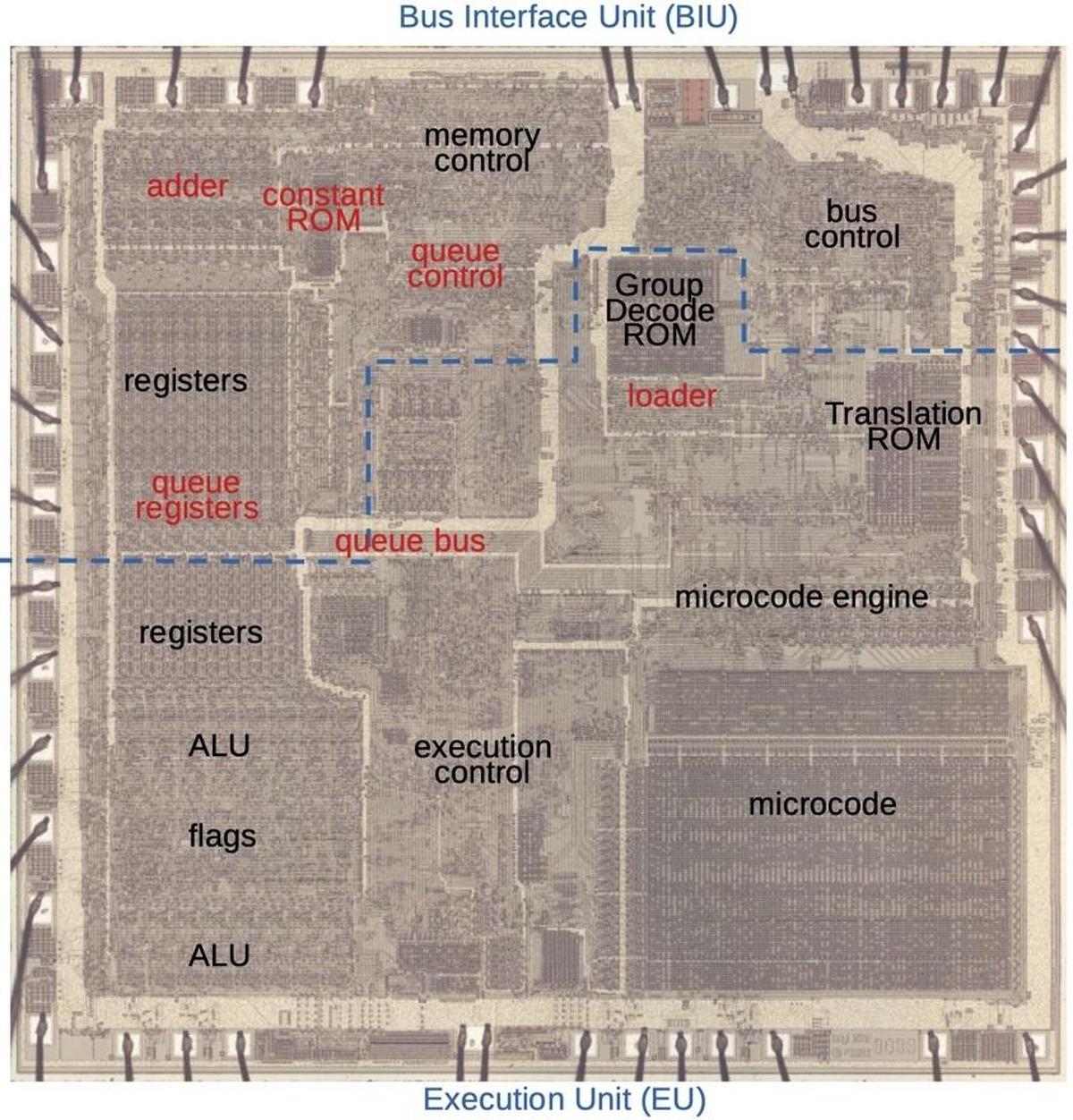

In 1993, Intel released the high-performance Pentium processor, the start of the long-running Pentium line. I've been examining the Pentium'...

It is often said that companies – particularly large companies with enormous IT budgets – do not buy products, they buy roadmaps. No one wants to go to

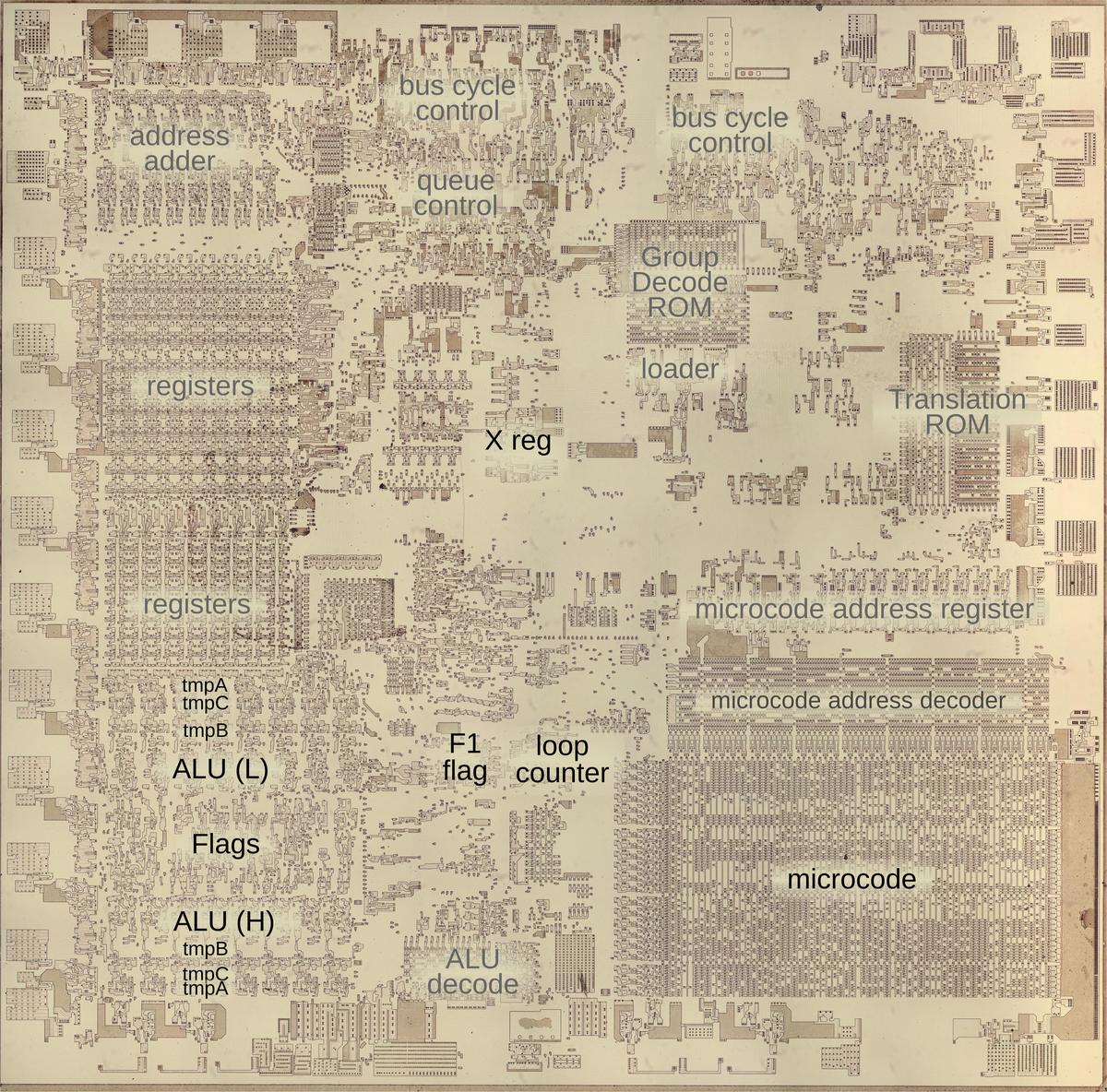

Intel released the powerful Pentium processor in 1993, establishing a long-running brand of high-performance processors. 1 The Pentium incl...

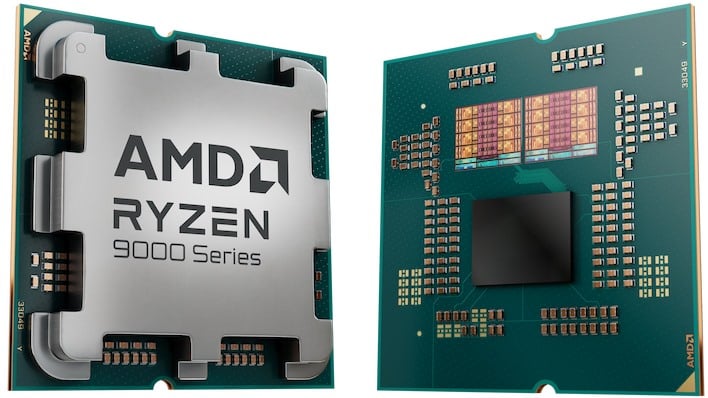

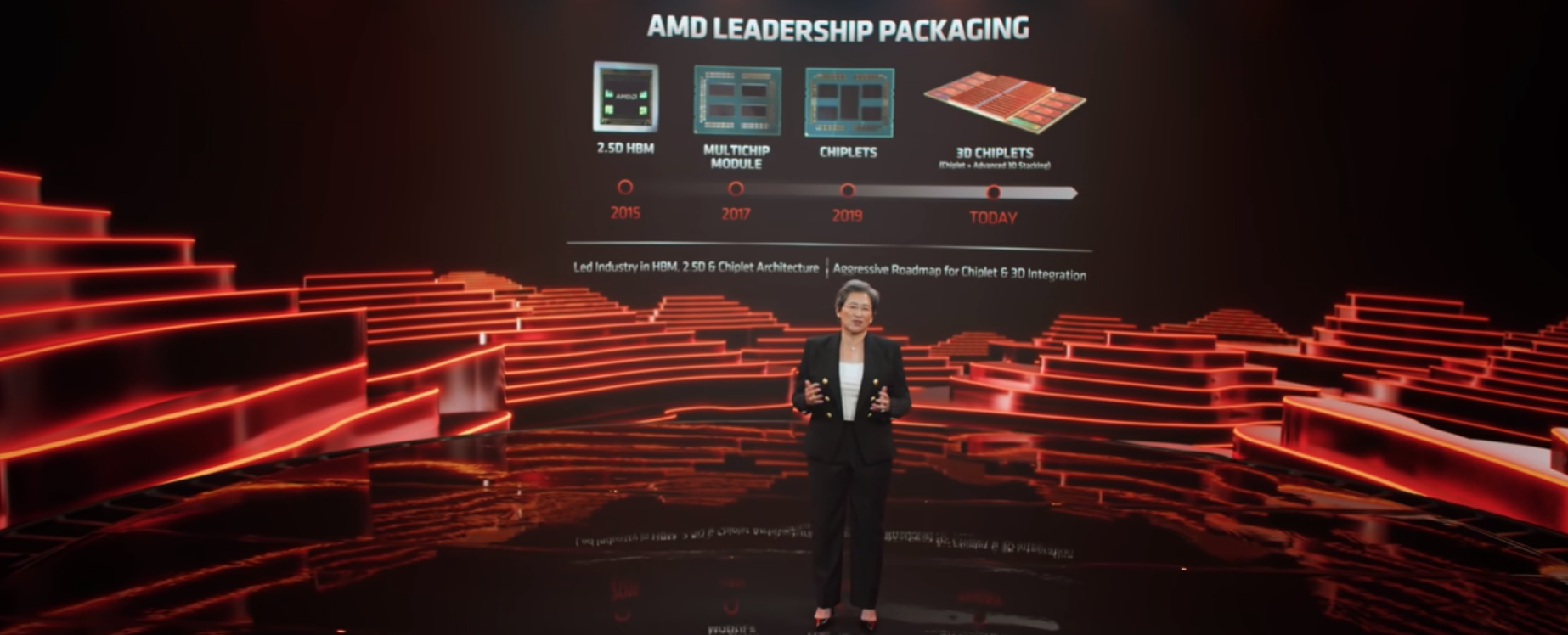

After persistent rumors refused to recede, AMD steps in with a clear explanation why dual-CCD V-Cache doesn't exist.

In 1993, Intel released the high-performance Pentium processor, the start of the long-running Pentium line. The Pentium had many improvement...

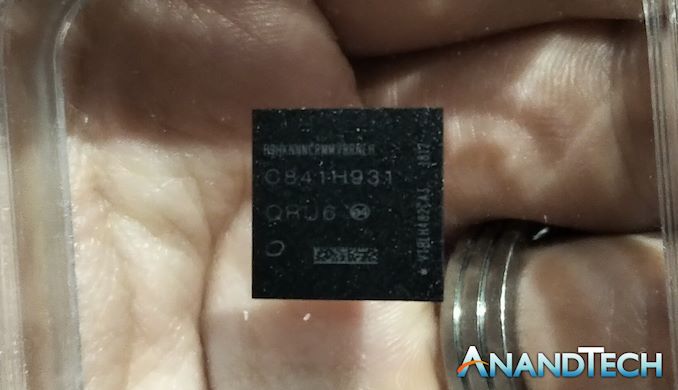

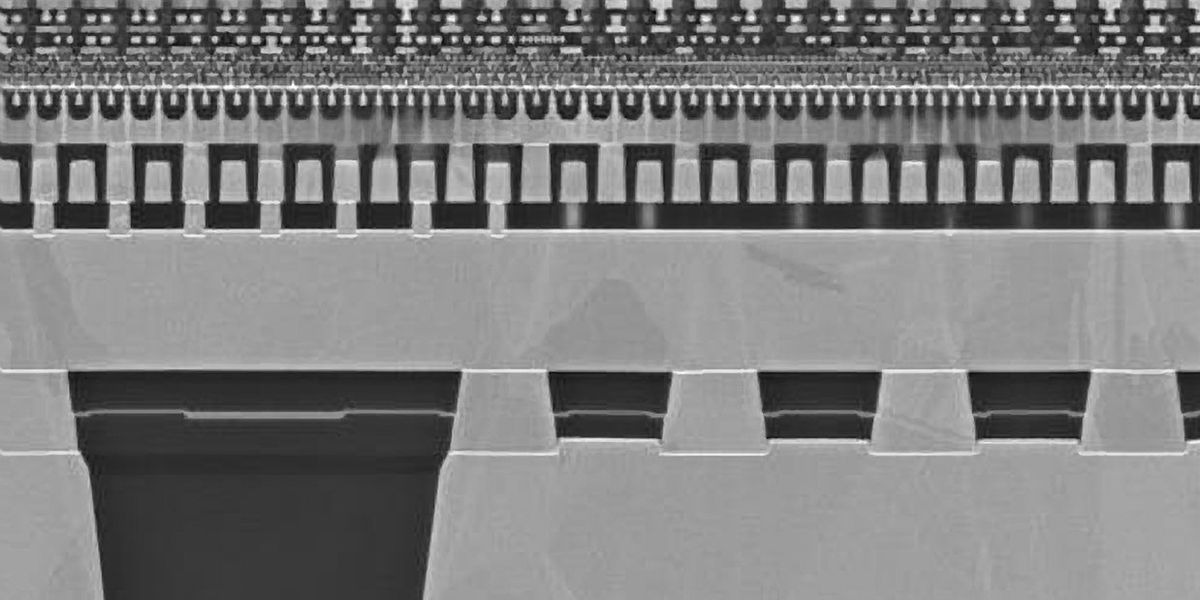

The CCD stack with 3D V-Cache on the AMD Ryzen 7 9800X3D is only 40-45µm in total, but the rest of the layers add up to a whopping 750µm.

I was studying the silicon die of the Pentium processor and noticed some puzzling structures where signal lines were connected to the silico...

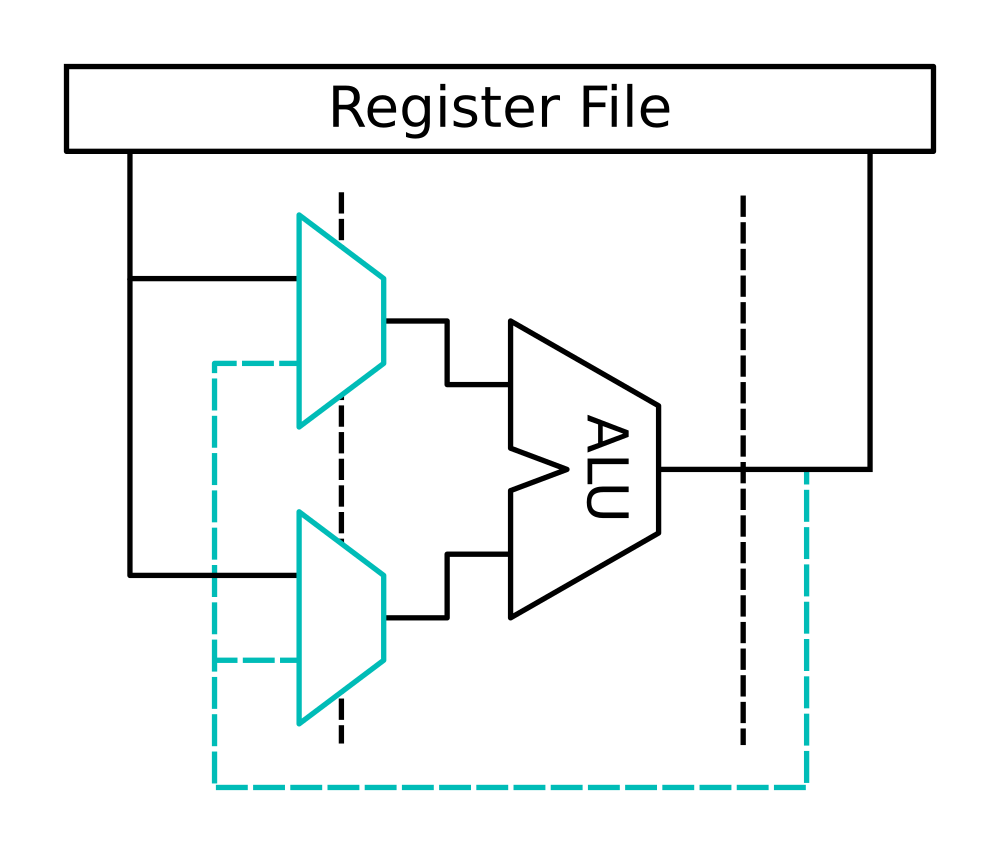

A loop buffer sits at a CPU's frontend, where it holds a small number of previously fetched instructions.

Intel was a dominant leader in the CPU market for the better part of a decade, but AMD has seen massive success in recent years thanks to its Ryzen chips.

Nitro, Graviton, EFA, Inferentia, Trainium, Nvidia Cloud, Microsoft Azure, Google Cloud, Oracle Cloud, Handicapping Infrastructure, AI As A Service, Enterprise Automation, Meta, Coreweave, TCO

No matter how elegant and clever the design is for a compute engine, the difficulty and cost of moving existing – and sometimes very old – code from the

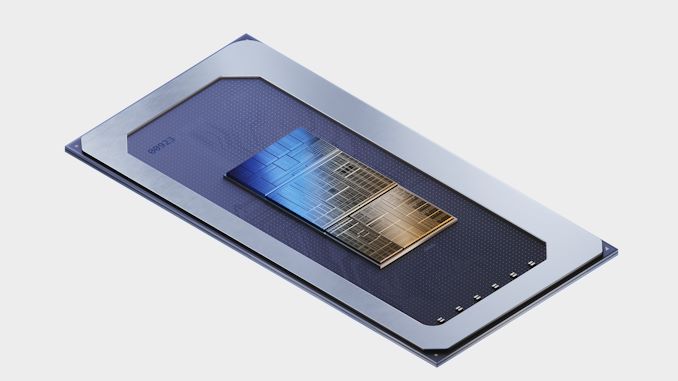

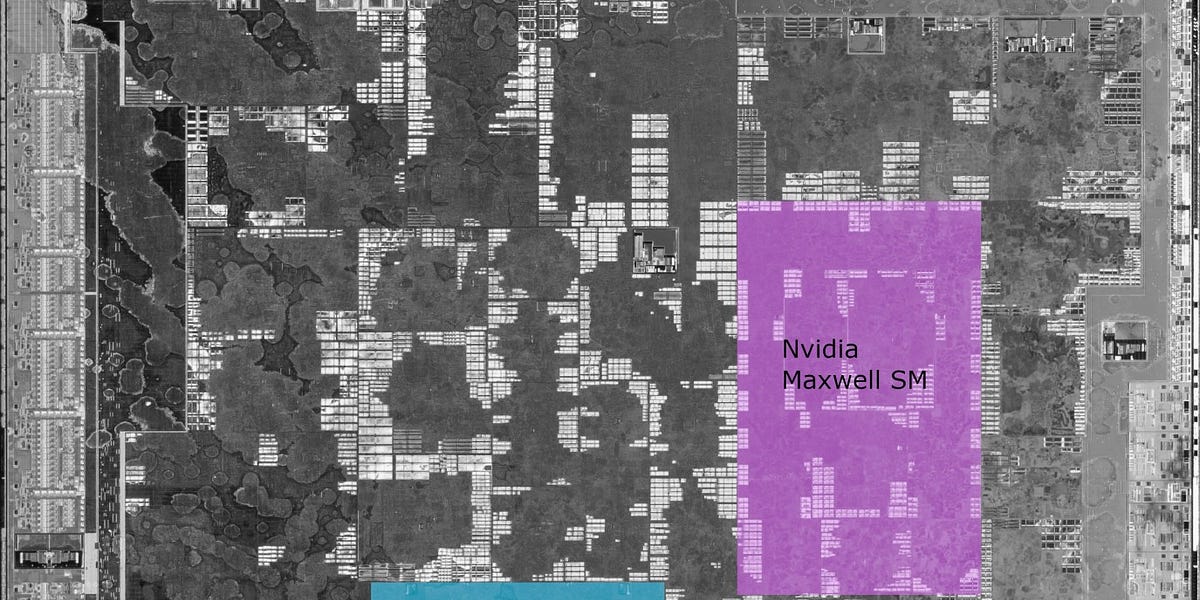

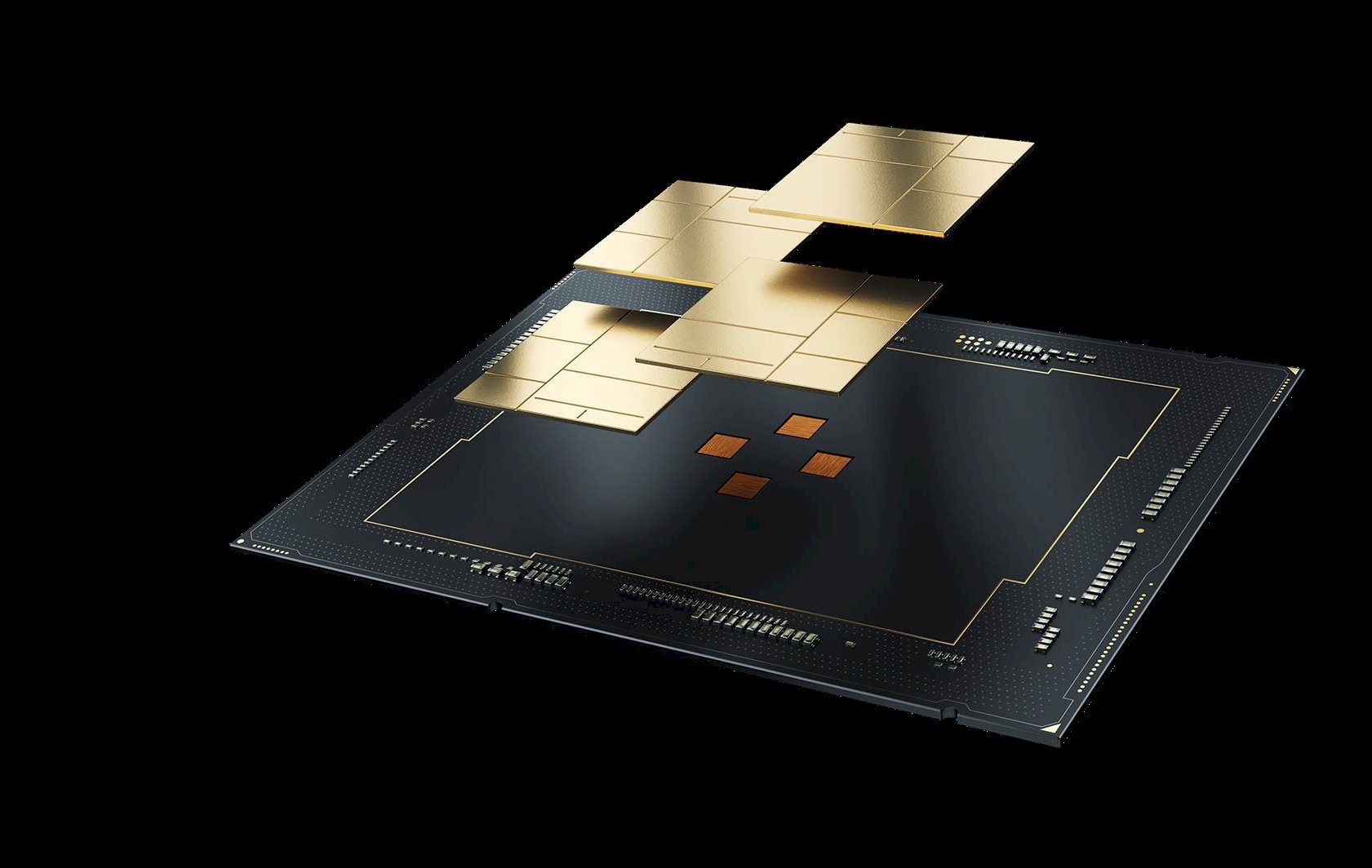

Intel’s Meteor Lake chip signaled a change in Intel’s mobile strategy, moving away from the monolithic designs that had characterized Intel’s client designs for more than a decade.

Intel's Core Ultra 200 "Arrow Lake" Desktop CPU specifications have now been finalized and we are just a month away from the official launch.

There are many chip partitioning and placement tradeoffs when comparing top-tier smartphone processor designs.

When I recently interviewed Mike Clark, he told me, “…you’ll see the actual foundational lift play out in the future on Zen 6, even though it was really Zen 5 that set the table for that.” And at that same Zen 5 architecture event, AMD’s Chief Technology Officer Mark Papermaster said, “Zen 5 is a ground-up redesign of the Zen architecture,” which has brought numerous and impactful changes to the design of the core.

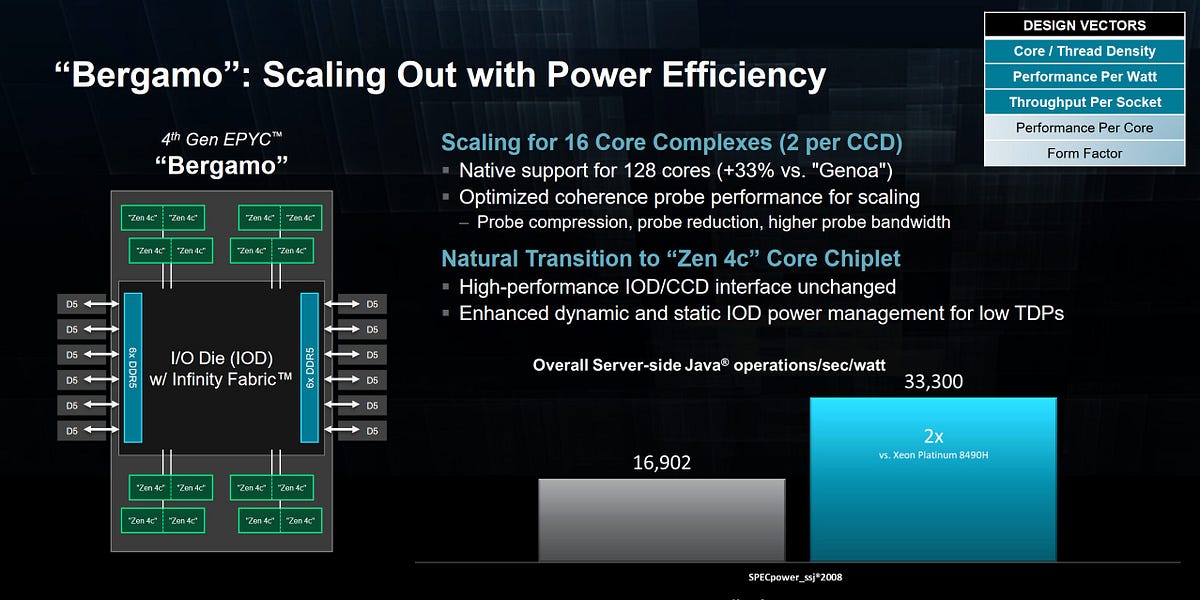

Server CPUs have pushed high core counts for a long time, though they way they got high core counts has varied.

A Finnish startup called Flow Computing is making one of the wildest claims ever heard in silicon engineering: by adding its proprietary companion chip,

192 cores, 385 threads, socket compatibility. What's not to like?

Anton Shilov reports via Tom's Hardware: About half of the processors packaged in Russia are defective. This has prompted Baikal Electronics, a Russian processor developer, to expand the number of packaging partners in the country, according to a report in Vedomosti, a Russian-language business dai...

Researchers also disclosed a separate bug called “Inception” for newer AMD CPUs.

Downfall attacks targets a critical weakness found in billions of modern processors used in personal and cloud computers.

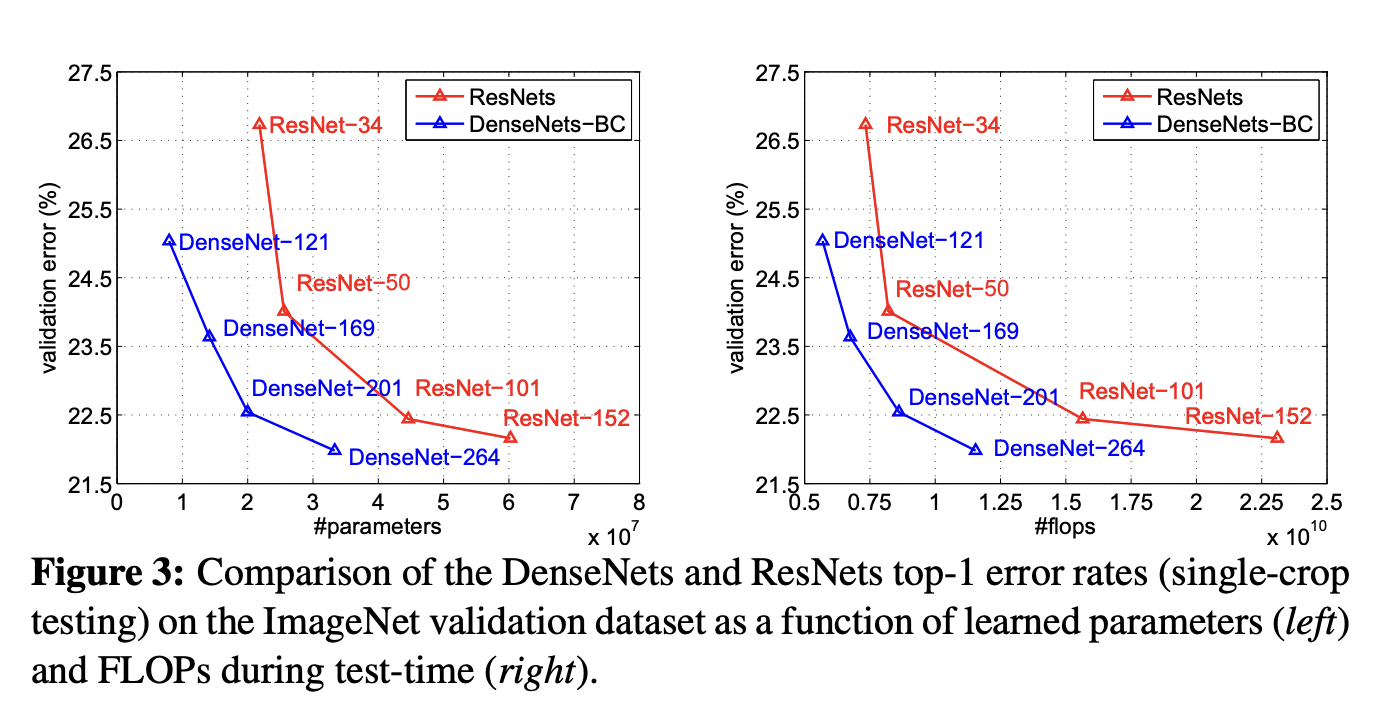

In this article we will learn about its definition, differences and how to calculate FLOPs and MACs using Python packages.

The company’s PowerVia interconnect tech demonstrated a 6 percent performance gain

GPUs may dominate, but CPUs could be perfect for smaller AI models

Tech enthusiasts probably know ARM as a company that develops reasonably performant CPU architectures with a focus on power efficiency.

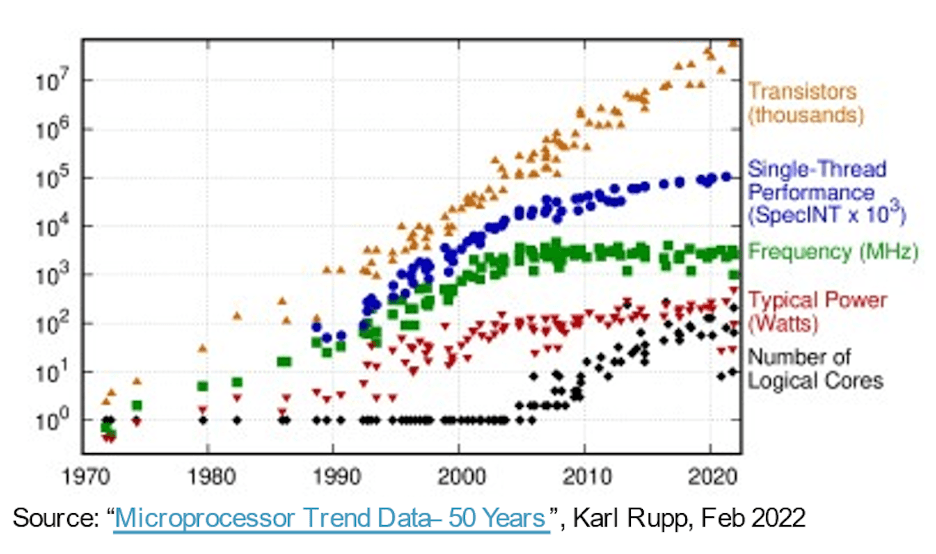

Over the past 10-15 years, per-core throughput increases have slowed, and in response CPU designers have scaled up core counts and socket counts to continue increasing performance across generations of new CPU models.

While programmers today take division for granted, most microprocessors in the 1970s could only add and subtract — division required a sl...

While microprocessors are used in various applications, they are precluded from the use in high-energy physics applications due to the harsh radiation present. To overcome this limitation a...

In the march to more capable, faster, smaller, and lower…

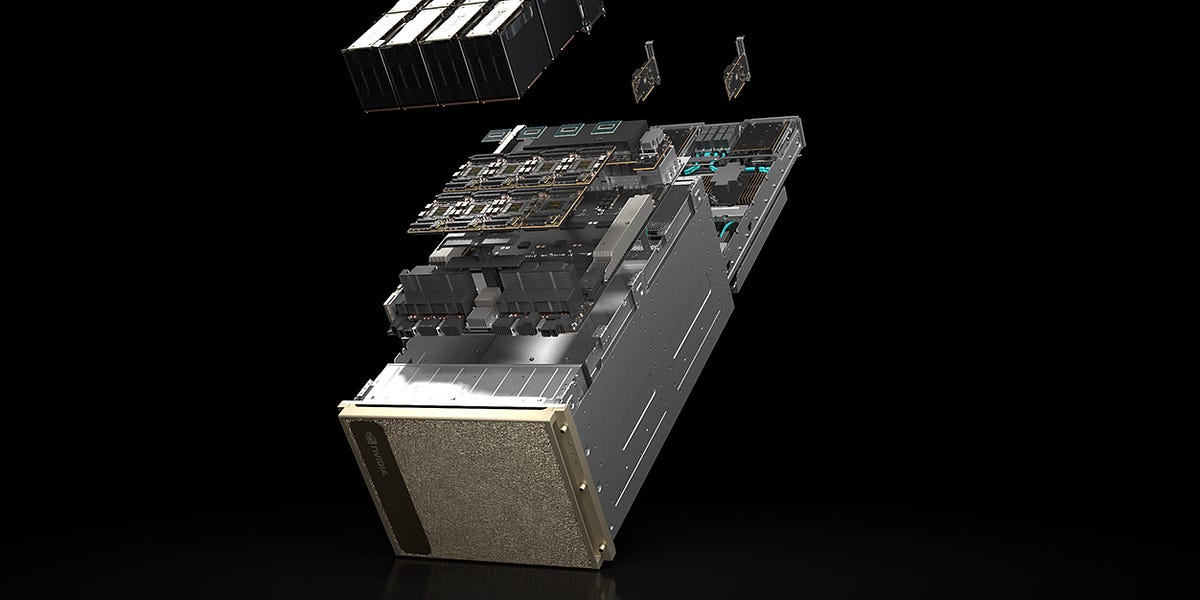

Sponsored Feature: Training an AI model takes an enormous amount of compute capacity coupled with high bandwidth memory. Because the model training can be

It was only a matter of time, perhaps, but the skyrocketing costs of designing chips is colliding with the ever-increasing need for performance,

Chinese chip designer Loongson, which has tried to reduce the country’s reliance on Intel and AMD, is developing its own general-purpose GPU despite being added to a US trade blacklist.

How to considerable reduce training time changing only 1 line of code

While Meta ups to five years

If a few cores are good, then a lot of cores ought to be better. But when it comes to HPC this isn’t always the case, despite what the Top500 ranking –

The groundbreaking 8086 microprocessor was introduced by Intel in 1978 and led to the x86 architecture that still dominates desktop and se...

Both companies are rolling out mitigations, but they add overhead of 12 to 28 percent.

Hertzbleed attack targets power-conservation feature found on virtually all modern CPUs.

HPC-oriented Latency Numbers Every Programmer Should Know · GitHub

In 2004 I was working for Microsoft in the Xbox group, and a new console was being created. I got a copy of the detailed descriptions of the Xbox 360 CPU and I read it through multiple times and su…

All CPU and MCU documentation in one place.

Nallatech doesn't make FPGAs, but it does have several decades of experience turning FPGAs into devices and systems that companies can deploy to solve

In this work, we analyze the performance of neural networks on a variety of heterogenous platforms. We strive to find the best platform in terms of raw benchmark performance, performance per watt a…

An accelerator unit improves both the performance and efficiency of a system by taking over one simple task

The CORE-V CVA6 is an Application class 6-stage RISC-V CPU capable of booting Linux - openhwgroup/cva6

Dozens of minimal operating systems to learn x86 system programming. Tested on Ubuntu 17.10 host in QEMU 2.10 and real hardware. Userland cheat at: https://github.com/cirosantilli/linux-kernel-modu...

Software optimization manuals for C++ and assembly code. Intel and AMD x86 microprocessors. Windows, Linux, BSD, Mac OS X. 16, 32 and 64 bit systems. Detailed descriptions of microarchitectures.

There are some features in any architecture that are essential, foundational, and non-negotiable. Right up to the moment that some clever architect shows

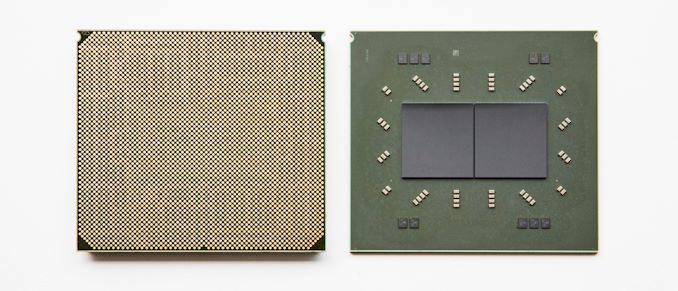

AMD recently unveiled 3D V-Cache, their first 3D-stacked technology-based product. Leapfrogging contemporary 3D bonding technologies, AMD jumped directly into advanced packaging with direct bonding and an order of magnitude higher wire density.

Although competition from Arm is increasing, AMD remains Intel’s biggest competitor, as concerns of losing market share weigh on Intel’s valuation.

A new CPU design has won accolades for defeating the hacking efforts of nearly 600 experts during a DARPA challenge. Its approach could help us close side-channel vulnerabilities in the future.

Apple is positioning its M1 quite differently from any CPU Intel or AMD has released. The long-term impact on the PC market could be significant.

Sapphire Rapids, Intel's next server architecture, looks like a large leap over the just-launched Ice Lake SP.

Rice University computer scientists have demonstrated artificial intelligence (AI) software that runs on commodity processors and trains deep neural networks 15 times faster than platforms based on graphics ...

The “Milan” Epyc 7003 processors, the third generation of AMD’s revitalized server CPUs, is now in the field, and we await the entry of the “Ice Lake”

AMD is one of the oldest designers of large scale microprocessors and has been the subject of polarizing debate among technology enthusiasts for nearly 50 years. Its...

With every passing year, as AMD first talked about its plans to re-enter the server processor arena and give Intel some real, much needed, and very direct

Understanding Intel® processor names and numbers helps identify the best laptop, desktop, or mobile device CPU for your computing needs.

There’s something really quite subtle about how the nproc utility from GNU coreutils works. If you look at the man page, it’s even the very first sentence: Print the number of processin…

In this article, I would like to shortly describe the methods used to dump and restore the different kinds of registers on 32-bit and 64-bit x86 CPUs. The first part will focus on General Purpose Registers, Debug Registers and Floating-Point Registers up to the XMM registers provided by the SSE extension. I will explain how their values can be obtained via the ptrace(2) interface.

They say "performance is king'... It was true a decade ago and it certainly is now. With more and mor...

When it comes to hashing, sometimes 64 bit is not enough, for example, because of birthday paradox — the hacker can iterate through random $latex 2^{32}$ entities and it can be proven that wi…

The x86 instruction set refers to the set of instructions that x86-compatible microprocessors support. The instructions are usually part of an executable program, often stored as a computer file and executed on the processor.

Fujitsu Limited today announced that it began shipping the supercomputer Fugaku, which is jointly developed with RIKEN and promoted by the Ministry of Education, Culture, Sports, Science and Technology with the aim of starting general operation between 2021 and 2022. The first machine to be shipped this time is one of the computer units of Fugaku, a supercomputer system comprised of over 150,000 high-performance CPUs connected together. Fujitsu will continue to deliver the units to RIKEN Center for Computational Science in Kobe, Japan, for installation and tuning.

Do the best you can until you know better. Then when you know better, do better. ― Maya Angelou

On the Linux command line it is fairly easy to use the perf command to measure number of floating point operations (or other performance metrics). (See for example this old blog post ) with this approach it is not easy to get a fine grained view of how different stages of processings within a single process. In this short note I describe how the python-papi package can be used to measure the FLOP requirements of any section of a Python program.

Recent leaks may shed some light on Intel's upcoming mainstream desktop Comet Lake-S CPUs.

Intel's Tremont CPU microarchitecture will be the foundation of a next-generation, low-power processors that target a wide variety of products across

A post describing how C programs get to the main function. Devicetree layouts, linker scripts, minimal C runtimes, GDB and QEMU, basic RISC-V assembly, and other topics are reviewed along the way.

Course overview Memory leaks and dangling pointers are the main issues of the manual memory management. You delete a parent node in a linked list, forgetting to delete all its children first -- and your

Excessive instruction cache misses are the kind of a performance problem that's going to appear only in larger codebases. In this article, I'm describing some ideas on how to deal with this issue.

Repository for the tools and non-commercial data used for the "Accelerator wall" paper. - PrincetonUniversity/accelerator-wall

Monday night Amazon announced the new 'A1' instance type for the Elastic Compute Cloud (EC2) that is powered by their own 'Graviton' ARMv8 processors.

It might have been difficult to see this happening a mere few years ago, but the National Nuclear Security Administration and one of its key

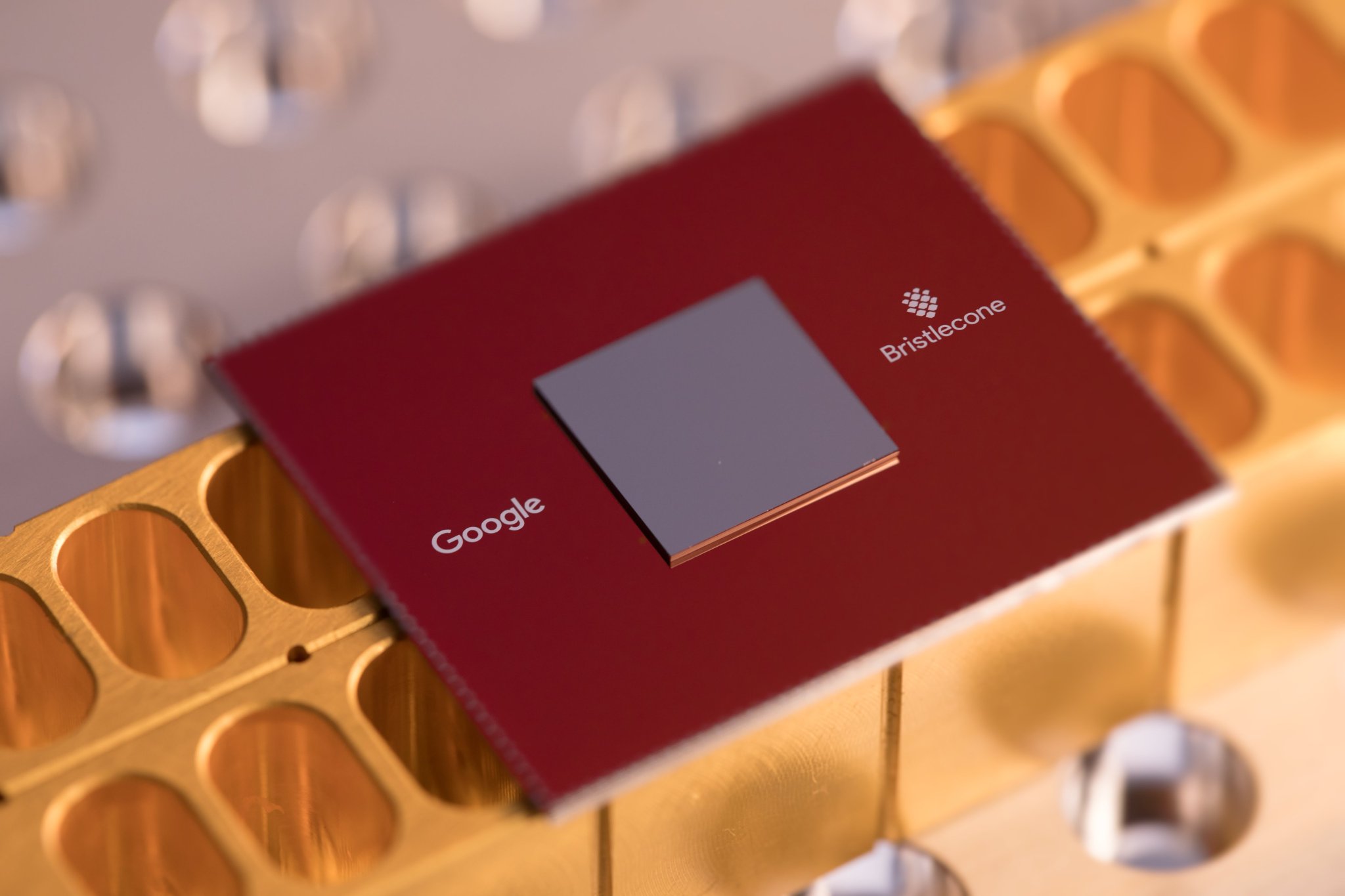

Every major tech company is looking at quantum computers as the next big breakthrough in computing. Teams at Google, Microsoft, Intel, IBM and various